동적 램

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

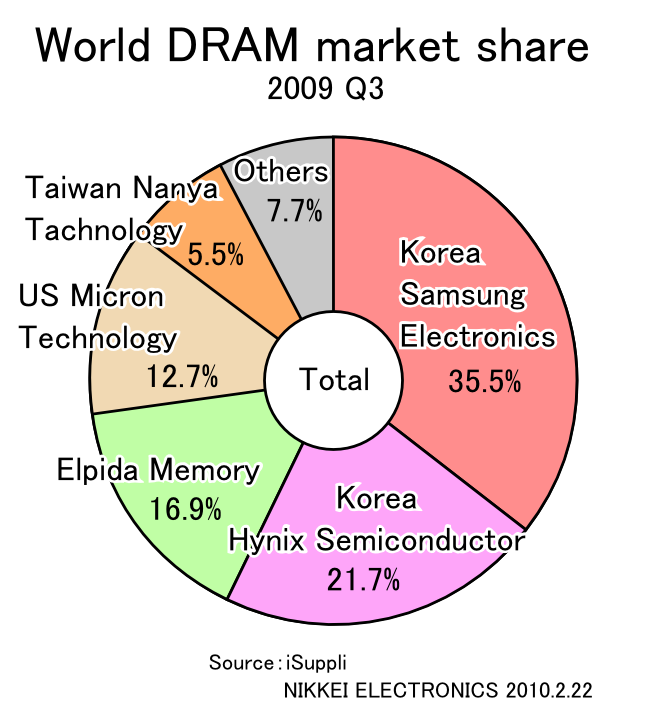

동적 램(DRAM)은 데이터를 저장하기 위해 커패시터와 트랜지스터를 사용하는 메모리 유형이다. 제2차 세계 대전 중 암호 해독 머신에 사용된 것이 시초이며, 1966년 로버트 데나드가 DRAM의 개념을 고안하고 특허를 받았다. 인텔은 1970년 최초의 DRAM 칩을 출시했다. DRAM은 비동기식에서 동기식(SDRAM)으로 발전했고, GDDR, PSRAM 등 다양한 종류가 있다. DRAM은 주기적인 리프레시가 필요하며, 데이터 잔류와 메모리 손상과 같은 보안 문제가 발생할 수 있다. 한국은 1980년대 후반부터 DRAM 산업에 진출하여 삼성전자와 SK하이닉스가 세계 시장을 선도하고 있다.

더 읽어볼만한 페이지

- 기억 장치 - EPROM

EPROM은 자외선을 사용하여 내용을 지울 수 있는 읽기 전용 메모리이며, MOSFET의 부유 게이트를 사용하여 데이터를 저장하고, 펌웨어 업데이트가 용이하여 소량 생산에 사용되었으나 EEPROM과 플래시 메모리에 의해 대체되었다. - 기억 장치 - 정적 램

정적 램(SRAM)은 전원이 공급되는 동안 데이터를 저장하며, 갱신 회로가 필요 없고 빠른 접근 속도를 가지는 휘발성 메모리 유형이다. - 20세기 발명품 - 텔레비전

텔레비전은 움직이는 영상과 소리를 전기 신호로 변환하여 전송하고 수신 측에서 다시 영상과 소리로 바꾸는 기술을 이용한 매체로, 닙코프 원판을 이용한 초기 기계식 방식에서 음극선관 발명을 통해 전자식으로 발전하여 디지털 기술과 다양한 디스플레이 기술 발전을 거쳐 현재에 이르렀으며 사회, 문화, 경제적으로 큰 영향을 미치지만 건강 문제 및 부정적 콘텐츠 노출 등의 부작용도 존재한다. - 20세기 발명품 - 태양 전지

태양전지는 빛 에너지를 전기 에너지로 변환하는 장치로, 기술 발전을 거듭하여 발전 효율이 크게 향상되었고 다양한 분야에 응용되고 있으며, 고집광 태양전지와 페로브스카이트 태양전지 등의 새로운 기술 개발과 투자가 지속적으로 요구되는 지속 가능한 에너지원이다. - 미국의 발명품 - 텔레비전

텔레비전은 움직이는 영상과 소리를 전기 신호로 변환하여 전송하고 수신 측에서 다시 영상과 소리로 바꾸는 기술을 이용한 매체로, 닙코프 원판을 이용한 초기 기계식 방식에서 음극선관 발명을 통해 전자식으로 발전하여 디지털 기술과 다양한 디스플레이 기술 발전을 거쳐 현재에 이르렀으며 사회, 문화, 경제적으로 큰 영향을 미치지만 건강 문제 및 부정적 콘텐츠 노출 등의 부작용도 존재한다. - 미국의 발명품 - 태양 전지

태양전지는 빛 에너지를 전기 에너지로 변환하는 장치로, 기술 발전을 거듭하여 발전 효율이 크게 향상되었고 다양한 분야에 응용되고 있으며, 고집광 태양전지와 페로브스카이트 태양전지 등의 새로운 기술 개발과 투자가 지속적으로 요구되는 지속 가능한 에너지원이다.

2. 역사

제2차 세계 대전 중 블레츨리 파크에서 사용된 코드명 Aquarius라는 암호 해독 머신은 고정 배선 형태의 동적 메모리를 장착하였다.

1964년, IBM의 아놀드 파버와 유진(Eugene Schlig)은 트랜지스터 게이트와 터널 다이오드 래치를 이용하여 고정 배선 형태의 메모리 셀을 만들었다. 이들은 래치를 두 개의 트랜지스터와 두 개의 레지스터로 대체하였으며, 이 구성은 Farber-Schlig 셀로 불렸다. 1965년, IBM의 벤자민 아구스타와 그의 팀은 이 Farber-Schlig 셀을 기반으로 80개의 트랜지스터, 64개의 레지스터, 4개의 다이오드가 포함된 16비트 실리콘 메모리 칩을 만들었다.

1966년, 로버트 H. 데나드 박사가 IBM 왓슨 연구소에서 DRAM을 발명하였다. 그는 1968년에 [https://web.archive.org/web/20151231134927/http://patft1.uspto.gov/netacgi/nph-Parser?patentnumber=3387286 3,387,286] 미국 특허를 받았다. DRAM은 캐패시터에 저장된 전하의 유무로 정보를 기억하지만, 이 전하는 시간이 지남에 따라 소실되므로 항상 전하를 갱신(리프레시)해야 한다. 이러한 "계속 움직이는" 특징에서 "다이내믹"(동적)이라는 이름이 붙었다. 뉴스 등에서는 "기억 유지 동작이 필요한 수시 쓰기/읽기 가능한 반도체 기억 회로" 등 긴 이름으로 소개되는 경우가 있다.

1970년 인텔은 세계 최초의 DRAM 칩인 1103을 제조했다. 1103은 3 트랜지스터 셀 설계를 사용한 1킬로비트 DRAM 칩이었다. 1970년대 중반까지 여러 제조업체가 데나드의 싱글 트랜지스터 셀을 사용하여 4킬로비트 칩을 제조했으며, 무어의 법칙에 따라 대용량화가 진전되었다.[69]

1970년대부터 1980년대 초기에 걸쳐, DRAM은 광범위하게 채택된 동작 규격 등이 존재하지 않아 DRAM 제품마다 세부적인 사양을 확인할 필요가 있었다. 또한, 2000년대에 일반화된 DIMM과 같은 메모리 모듈 형태의 구현은 소수에 불과했으며, 대부분 단품 DIP를 8개 또는 16개 등 여러 개를 개별적으로 DIP 소켓에 삽입하여 구현했다.

2. 1. 초기 발전

제2차 세계 대전 중 블레츨리 파크에서 사용된 암호 해독기 'Aquarius'는 하드 와이어드 동적 메모리를 사용했다. 이 메모리는 대규모 커패시터 뱅크를 사용하여 데이터를 저장했으며, 주기적인 펄스로 커패시터를 재충전하여 데이터를 유지했다.[5]1964년, IBM의 아놀드 파버와 유진 슐리그는 트랜지스터와 터널 다이오드 래치를 이용한 고정 배선 메모리 셀을 개발했다. 이들은 래치를 두 개의 트랜지스터와 두 개의 레지스터로 대체하여 'Farber-Schlig 셀'을 만들었다. 1965년, IBM의 벤자민 아구스타와 그의 팀은 이 셀을 기반으로 16비트 실리콘 메모리 칩을 제작했다.

1966년, IBM 왓슨 연구소의 로버트 H. 데나드 박사가 DRAM을 발명했다. 그는 1968년에 이 발명에 대한 미국 특허를 받았다.[13] 데나드 박사의 DRAM은 각 캐패시터마다 단일 MOS 트랜지스터를 사용하는 현대 DRAM 아키텍처를 기반으로 한다. 그는 MOS 기술의 특성을 조사하던 중, 캐패시터에 전하를 저장하거나 저장하지 않는 방식으로 비트의 1과 0을 나타낼 수 있고, MOS 트랜지스터가 전하를 쓰는 것을 제어할 수 있다는 것을 발견했다. 이를 통해 단일 트랜지스터 MOS DRAM 메모리 셀이 개발되었다.[12]

2. 2. 상용화 및 발전

1970년 인텔(Intel Corporation)은 세계 최초의 상용 DRAM 칩인 1103을 출시했다.[69] 1103은 1킬로비트 DRAM 칩으로, 매우 성공적이었다. 1973년 모스텍(Mostek)은 다중화된 행과 열 주소 지정 방식을 사용한 최초의 DRAM인 MK4096(4 Kbit)을 출시했다. 이 방식은 동일한 주소 핀으로 메모리 셀 주소의 상위 절반과 하위 절반을 번갈아 수신하여, 필요한 주소 라인 수를 절반으로 줄였다. 이는 더 적은 핀을 가진 패키지에 DRAM을 실장할 수 있게 하여 메모리 용량 증가에 따른 비용 이점을 제공했다.1980년대에는 일본 DRAM 제조업체들이 미국 및 전 세계 시장을 지배했다. 그러나 1985년 초, 고든 무어(Gordon Moore)는 인텔의 DRAM 생산 중단을 결정했고,[20] 1986년까지 많은 미국 칩 제조업체들이 DRAM 생산을 중단했다.[21]

1990년대 이후 삼성(Samsung)을 필두로 한국 기업들이 DRAM 시장에서 부상했다. 삼성은 동기식 동적 램(SDRAM)을 개발했다. 최초의 상업용 SDRAM 칩은 1992년 출시된 삼성 KM48SL2000(16 Mb)이었고,[23][24] 최초의 상업용 DDR SDRAM (더블 데이터 레이트 SDRAM) 메모리 칩은 1998년에 출시된 삼성의 64 Mb DDR SDRAM 칩이었다.[25] 현재는 삼성전자와 SK하이닉스가 세계 DRAM 시장을 선도하고 있다.

3. 종류 및 기술 발전

동적 램(DRAM)은 시간이 지남에 따라 다양한 종류와 기술 발전이 이루어졌다.

=== 비동기 DRAM ===

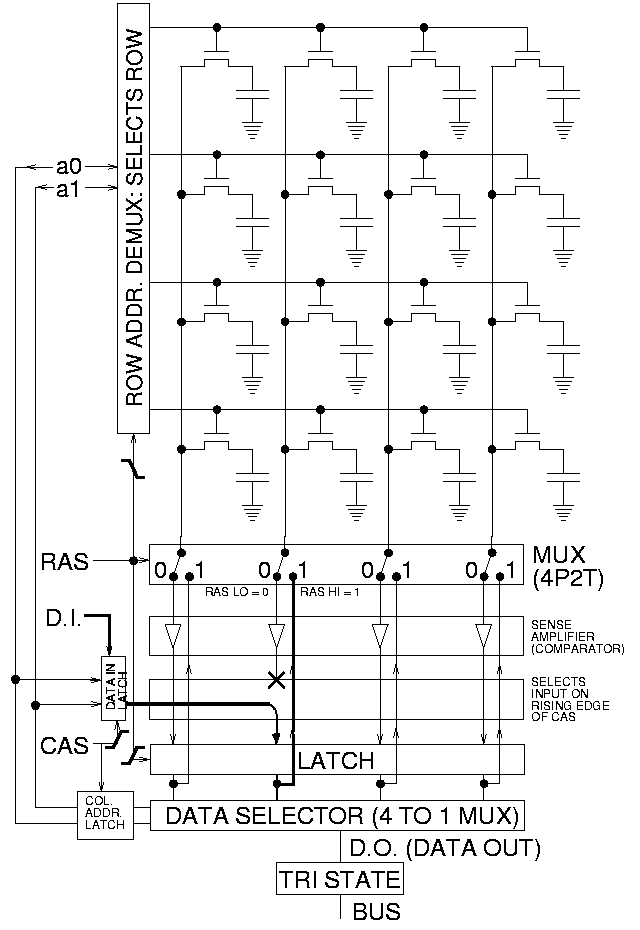

초기 DRAM은 비동기식으로 작동했으며, RAS , CAS, WE 등의 제어 신호를 사용했다.[51] 이러한 비동기식 DRAM은 전원 연결, 주소 입력, 양방향 데이터 라인, 그리고 RAS (로우 어드레스 스트로브), CAS (컬럼 어드레스 스트로브), WE (쓰기 활성화)와 같은 주요 제어 신호를 가진다.

데이터 저장을 위해 행이 열리고, 특정 열의 감지 증폭기가 원하는 전압 상태로 강제되어 비트 라인이 셀 저장 커패시터를 충전하거나 방전시킨다. 감지 증폭기의 정귀환 구성으로 인해 강제 전압이 제거된 후에도 비트 라인을 안정적인 전압으로 유지한다.[29]

일반적으로 제조업체는 JEDEC 표준에 따라 각 행을 64ms 이하마다 리프레시해야 한다고 명시한다. 일부 조건에서는 DRAM이 몇 분 동안 리프레시되지 않았더라도 DRAM의 대부분의 데이터를 복구할 수 있다.[30]

DRAM 작동 타이밍은 여러 매개변수로 설명된다. 다음은 1998년 데이터 시트에서 가져온 비동기 DRAM의 타이밍 예시다.[31]

100 MHz 상태 머신에 의해 액세스되는 경우, 50 ns DRAM은 5개의 클럭 사이클로 첫 번째 읽기를 수행할 수 있으며, 동일한 페이지 내의 추가 읽기는 2개의 클럭 사이클마다 수행할 수 있다. 이는 "5-2-2-2" 타이밍으로 설명된다.

'''페이지 모드 DRAM'''은 1세대 DRAM IC 인터페이스의 작은 수정으로, 동일한 행에 대한 읽기 및 쓰기 성능을 향상시켰다. 페이지 모드 DRAM에서는 행이 열린 후, 해당 행의 임의의 열에 대해 여러 번의 읽기 또는 쓰기를 수행할 수 있다.[56]

페이지 모드 DRAM은 이후 약간의 수정을 통해 대기 시간을 더욱 줄여 성능을 향상시켰다. 이러한 개선 사항이 적용된 DRAM을 '''고속 페이지 모드 DRAM''' ('''FPM DRAM''')이라고 한다. FPM DRAM에서는 CAS가 아직 비활성화된 상태에서도 열 주소를 제공할 수 있으며, 주요 열 접근 시간은 주소가 안정되는 즉시 시작된다.[57] 고속 페이지 모드 DRAM은 1986년에 도입되었으며 인텔 80486과 함께 사용되었다.

thumb EDO DRAM 모듈 한 쌍]]

'''EDO DRAM''' (확장 데이터 출력 DRAM)은 1990년대에 마이크론 테크놀로지에 의해 발명되고 특허를 받았다.[58] EDO DRAM은 새로운 액세스 사이클을 시작할 수 있는 추가 기능을 가진 고속 페이지 모드 DRAM과 유사하다.[59] 이는 FPM DRAM보다 최대 30% 빠르며,[60] 1995년에 FPM DRAM을 대체하기 시작했다.

'''BEDO DRAM''' (버스트 EDO DRAM)은 한 번의 버스트로 4개의 메모리 주소를 처리하여 최대 5-1-1-1의 속도를 낼 수 있었고, 최적 설계된 EDO 메모리에 비해 3 클럭을 더 절약했다. BEDO DRAM은 SDRAM에 의해 대체되었다.[63]

=== 동기 DRAM (SDRAM) ===

SDRAM(동기식 D램, Synchronous DRAM)은 외부 클럭 신호에 맞춰 작동하는 DRAM이다. 클럭 신호를 사용하여 DRAM 내부 동작을 동기화하고, 이를 통해 데이터 전송 속도를 높였다.

SDRAM은 여러 개의 내부 뱅크를 가지고 있어, 한 뱅크에서 데이터를 읽는 동안 다른 뱅크를 활성화하여 데이터를 준비할 수 있다. 이러한 방식으로 데이터 버스를 효율적으로 사용하여 성능을 향상시켰다.[72]

SDRAM의 주요 특징은 다음과 같다:

- 동기식 인터페이스: 클럭 신호에 맞춰 모든 신호가 입력되고 출력된다.

- 명령 제어: RAS 및 CAS 신호는 더 이상 스트로브가 아니라 CS 신호와 함께 3비트 명령의 일부로 사용된다.

- 데이터 입출력 제어: WE 신호의 기능이 확장되어 DQM 신호가 데이터 출력(읽기)뿐만 아니라 데이터 입력(쓰기)도 제어한다.

- 타이밍 매개변수: DRAM 컨트롤러가 제어하는 다양한 타이밍 매개변수(예: CAS 대기 시간)가 있다.

SDRAM은 다음과 같이 여러 세대로 발전해왔다:

- SDR SDRAM (Single Data Rate SDRAM): SDRAM의 첫 번째 세대로, 클럭 사이클당 한 번의 데이터 전송을 수행한다.

- DDR SDRAM (Double Data Rate SDRAM): 클럭 신호의 상승 및 하강 에지 모두에서 데이터를 전송하여 SDR SDRAM보다 2배 빠른 속도를 제공한다. 2000년부터 PC 메모리에 사용되기 시작했다.[76]

- DDR2 SDRAM: DDR SDRAM을 개선하여 더 높은 클럭 속도와 향상된 파이프라이닝을 제공한다.

- DDR3 SDRAM: DDR2 SDRAM보다 더 높은 속도와 낮은 전력 소비를 제공한다.

- DDR4 SDRAM, DDR5 SDRAM: 지속적으로 발전하여 더 빠른 속도와 대역폭을 제공한다.

=== 기타 DRAM 종류 ===

VRAM은 듀얼 포트된 버전의 DRAM으로, 이전에는 그래픽 어댑터 안에서 비트맵(프레임 버퍼)을 저장하는 데 사용되기도 했다. WRAM(윈도 램)은 그래픽 어댑터의 VRAM을 대체하기 위해 삼성에서 개발하고 마이크론 테크놀로지에서 상용화한 메모리이다. 그러나 WRAM은 SDRAM과 SGRAM에게 밀려 시장에서 단명했다.

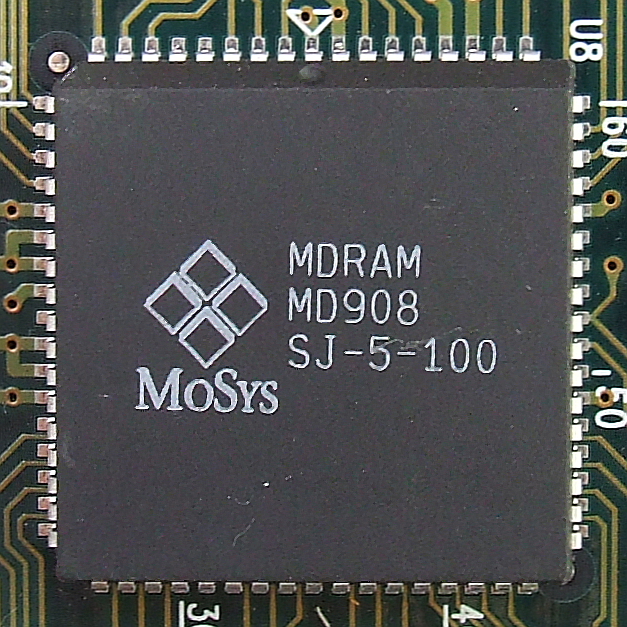

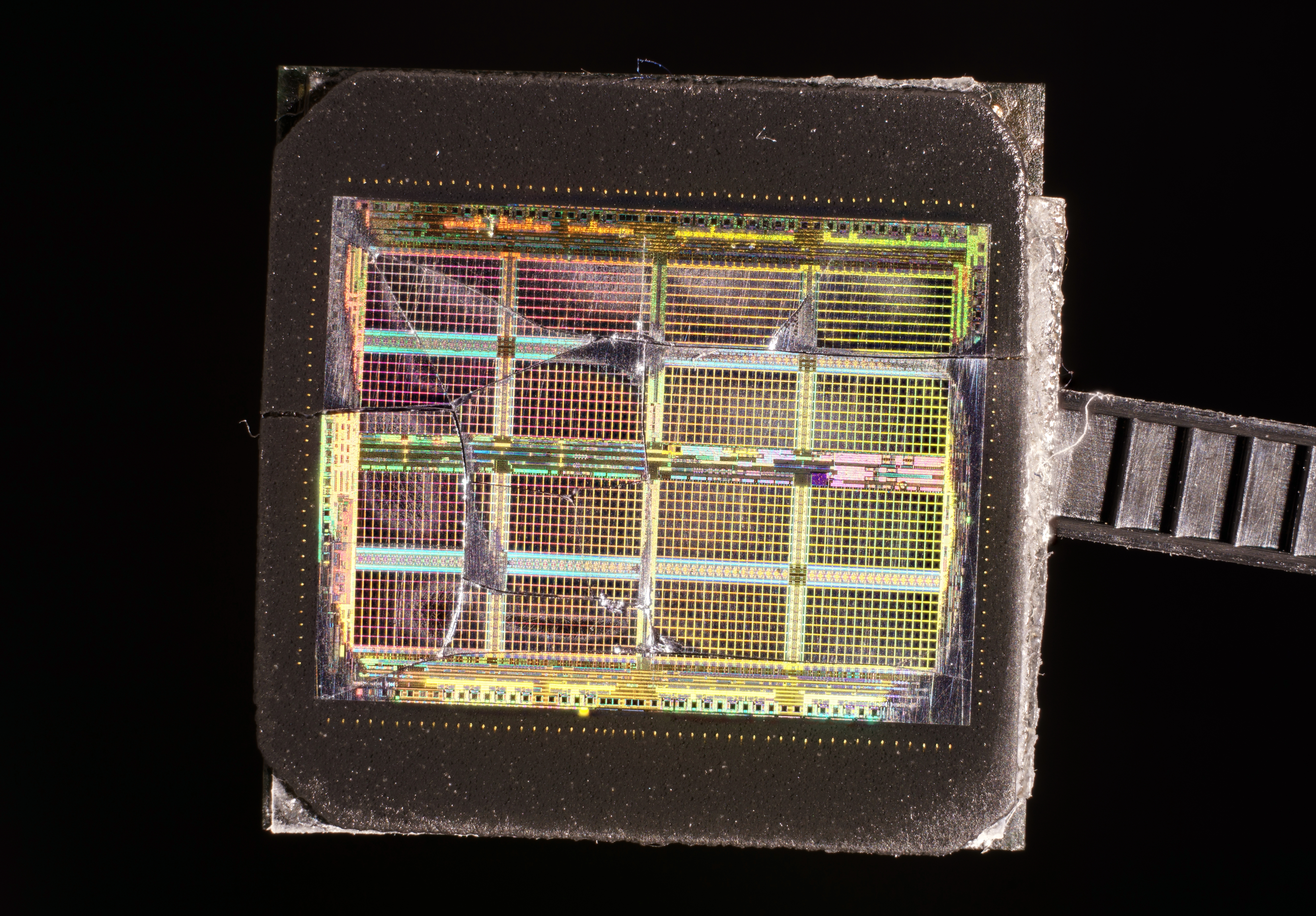

MDRAM(멀티뱅크 DRAM)은 MoSys에서 개발한 특수 DRAM이다. MDRAM은 256 kB의 작은 메모리 뱅크로 구성되어 인터리빙 방식으로 작동하므로, SRAM보다 저렴한 비용으로 그래픽 카드에 적합한 대역폭을 제공한다. MDRAM은 단일 클럭 사이클에 두 뱅크에서 연산을 허용하여, 접근이 독립적인 경우 여러 동시 접근이 가능하다. MDRAM은 주로 Tseng Labs ET6x00 칩셋을 탑재한 그래픽 카드에 사용되었다.

SGRAM(동기식 그래픽스 램)은 그래픽 어댑터를 위한 특수 형태의 SDRAM이다. 비트 마스크 기능(다른 비트 평면에 영향을 주지 않고 특정 비트 평면에 쓰기)과 블록 쓰기(단일 색상으로 메모리 블록 채우기)와 같은 기능을 추가한다. VRAM 및 WRAM과 달리 SGRAM은 단일 포트이지만, 두 개의 메모리 페이지를 동시에 열어 다른 비디오 램 기술의 듀얼 포트 특성을 흉내낼 수 있다.

GDDR SDRAM(그래픽스 더블 데이터 레이트 SDRAM)은 DDR SDRAM의 특수한 유형으로, GPU의 주 메모리로 사용하도록 설계되었다. GDDR SDRAM은 DRAM 코어와 I/O 인터페이스 모두 더 높은 클럭 주파수를 가져 GPU에 더 큰 메모리 대역폭을 제공한다는 점이 특징이다. 2020년 현재, GDDR2, GDDR3, GDDR4, GDDR5, GDDR5X, GDDR6 및 GDDR6X의 7개의 연속적인 GDDR 세대가 있다.

PSRAM(유사 정적 램)은 내장된 리프레시 및 주소 제어 회로를 갖춘 동적 램으로, 정적 램(SRAM)과 유사하게 작동한다. DRAM의 높은 집적도와 진정한 SRAM의 사용 편의성을 결합했다. PSRAM은 애플 아이폰(Apple iPhone) 및 XFlar 플랫폼과 같은 임베디드 시스템에 사용된다.[65]

RLDRAM(감소된 레이턴시 디램)은 높은 대역너비와 더불어 속도가 빠른, 랜덤 액세스를 제공하는 DDR SDRAM이다. RLDRAM은 주로 네트워크 응용 프로그램이나 캐시 응용 프로그램에 쓰일 것을 염두에 두고 설계되었다.

3. 1. 비동기 DRAM

초기 DRAM은 비동기식으로 작동했으며, , , 등의 제어 신호를 사용했다.[51] 이러한 비동기식 DRAM은 전원 연결, 주소 입력, 양방향 데이터 라인, 그리고 (로우 어드레스 스트로브), (컬럼 어드레스 스트로브), (쓰기 활성화)와 같은 주요 제어 신호를 가진다.데이터 저장을 위해 행이 열리고, 특정 열의 감지 증폭기가 원하는 전압 상태로 강제되어 비트 라인이 셀 저장 커패시터를 충전하거나 방전시킨다. 감지 증폭기의 정귀환 구성으로 인해 강제 전압이 제거된 후에도 비트 라인을 안정적인 전압으로 유지한다.[29]

일반적으로 제조업체는 JEDEC 표준에 따라 각 행을 64ms 이하마다 리프레시해야 한다고 명시한다. 일부 조건에서는 DRAM이 몇 분 동안 리프레시되지 않았더라도 DRAM의 대부분의 데이터를 복구할 수 있다.[30]

DRAM 작동 타이밍은 여러 매개변수로 설명된다. 다음은 1998년 데이터 시트에서 가져온 비동기 DRAM의 타이밍 예시다.[31]

이러한 RAM이 클럭 논리에 의해 액세스될 때, 시간은 일반적으로 가장 가까운 클럭 사이클로 반올림된다. 예를 들어, 100 MHz 상태 머신에 의해 액세스되는 경우, 50 ns DRAM은 5개의 클럭 사이클로 첫 번째 읽기를 수행할 수 있으며, 동일한 페이지 내의 추가 읽기는 2개의 클럭 사이클마다 수행할 수 있다. 이는 "5-2-2-2" 타이밍으로 설명된다.

'''페이지 모드 DRAM'''은 1세대 DRAM IC 인터페이스의 작은 수정으로, 동일한 행에 대한 읽기 및 쓰기 성능을 향상시킨다. 페이지 모드 DRAM에서는 행이 열린 후, 해당 행의 임의의 열에 대해 여러 번의 읽기 또는 쓰기를 수행할 수 있다.[56]

페이지 모드 DRAM은 이후 약간의 수정을 통해 대기 시간을 더욱 줄여 성능을 향상시켰다. 이러한 개선 사항이 적용된 DRAM을 '''고속 페이지 모드 DRAM''' ('''FPM DRAM''')이라고 한다. FPM DRAM에서는 가 아직 비활성화된 상태에서도 열 주소를 제공할 수 있으며, 주요 열 접근 시간은 주소가 안정되는 즉시 시작된다.[57] 고속 페이지 모드 DRAM은 1986년에 도입되었으며 인텔 80486과 함께 사용되었다.

thumb EDO DRAM 모듈 한 쌍]]

'''EDO DRAM''' (확장 데이터 출력 DRAM)은 1990년대에 마이크론 테크놀로지에 의해 발명되고 특허를 받았다.[58] EDO DRAM은 새로운 액세스 사이클을 시작할 수 있는 추가 기능을 가진 고속 페이지 모드 DRAM과 유사하다.[59] 이는 FPM DRAM보다 최대 30% 빠르며,[60] 1995년에 FPM DRAM을 대체하기 시작했다.

'''BEDO DRAM''' (버스트 EDO DRAM)은 한 번의 버스트로 4개의 메모리 주소를 처리하여 최대 5-1-1-1의 속도를 낼 수 있었고, 최적 설계된 EDO 메모리에 비해 3 클럭을 더 절약했다. BEDO DRAM은 SDRAM에 의해 대체되었다.[63]

3. 2. 동기 DRAM (SDRAM)

SDRAM(동기식 D램, Synchronous DRAM)은 외부 클럭 신호에 맞춰 작동하는 DRAM이다. 클럭 신호를 사용하여 DRAM 내부 동작을 동기화하고, 이를 통해 데이터 전송 속도를 높였다.SDRAM은 여러 개의 내부 뱅크를 가지고 있어, 한 뱅크에서 데이터를 읽는 동안 다른 뱅크를 활성화하여 데이터를 준비할 수 있다. 이러한 방식으로 데이터 버스를 효율적으로 사용하여 성능을 향상시켰다.[72]

SDRAM의 주요 특징은 다음과 같다:

- 동기식 인터페이스: 클럭 신호에 맞춰 모든 신호가 입력되고 출력된다.

- 명령 제어: 및 신호는 더 이상 스트로브가 아니라 신호와 함께 3비트 명령의 일부로 사용된다.

- 데이터 입출력 제어: 신호의 기능이 확장되어 DQM 신호가 데이터 출력(읽기)뿐만 아니라 데이터 입력(쓰기)도 제어한다.

- 타이밍 매개변수: DRAM 컨트롤러가 제어하는 다양한 타이밍 매개변수(예: CAS 대기 시간)가 있다.

SDRAM은 다음과 같이 여러 세대로 발전해왔다:

- SDR SDRAM (Single Data Rate SDRAM): SDRAM의 첫 번째 세대로, 클럭 사이클당 한 번의 데이터 전송을 수행한다.

- DDR SDRAM (Double Data Rate SDRAM): 클럭 신호의 상승 및 하강 에지 모두에서 데이터를 전송하여 SDR SDRAM보다 2배 빠른 속도를 제공한다. 2000년부터 PC 메모리에 사용되기 시작했다.[76]

- DDR2 SDRAM: DDR SDRAM을 개선하여 더 높은 클럭 속도와 향상된 파이프라이닝을 제공한다.

- DDR3 SDRAM: DDR2 SDRAM보다 더 높은 속도와 낮은 전력 소비를 제공한다.

- DDR4 SDRAM, DDR5 SDRAM: 지속적으로 발전하여 더 빠른 속도와 대역폭을 제공한다.

3. 3. 기타 DRAM 종류

VRAM은 듀얼 포트된 버전의 DRAM으로, 이전에는 그래픽 어댑터 안에서 비트맵(프레임 버퍼)을 저장하는 데 사용되기도 했다. WRAM(윈도 램)은 그래픽 어댑터의 VRAM을 대체하기 위해 삼성에서 개발하고 마이크론 테크놀로지에서 상용화한 메모리이다. 그러나 WRAM은 SDRAM과 SGRAM에게 밀려 시장에서 단명했다.MDRAM(멀티뱅크 DRAM)은 MoSys에서 개발한 특수 DRAM이다. MDRAM은 256 kB의 작은 메모리 뱅크로 구성되어 인터리빙 방식으로 작동하므로, SRAM보다 저렴한 비용으로 그래픽 카드에 적합한 대역폭을 제공한다. MDRAM은 단일 클럭 사이클에 두 뱅크에서 연산을 허용하여, 접근이 독립적인 경우 여러 동시 접근이 가능하다. MDRAM은 주로 Tseng Labs ET6x00 칩셋을 탑재한 그래픽 카드에 사용되었다.

SGRAM(동기식 그래픽스 램)은 그래픽 어댑터를 위한 특수 형태의 SDRAM이다. 비트 마스크 기능(다른 비트 평면에 영향을 주지 않고 특정 비트 평면에 쓰기)과 블록 쓰기(단일 색상으로 메모리 블록 채우기)와 같은 기능을 추가한다. VRAM 및 WRAM과 달리 SGRAM은 단일 포트이지만, 두 개의 메모리 페이지를 동시에 열어 다른 비디오 램 기술의 듀얼 포트 특성을 흉내낼 수 있다.

GDDR(그래픽스 더블 데이터 레이트) SDRAM은 DDR SDRAM의 특수한 유형으로, GPU의 주 메모리로 사용하도록 설계되었다. GDDR SDRAM은 DRAM 코어와 I/O 인터페이스 모두 더 높은 클럭 주파수를 가져 GPU에 더 큰 메모리 대역폭을 제공한다는 점이 특징이다. 2020년 현재, GDDR2, GDDR3, GDDR4, GDDR5, GDDR5X, GDDR6 및 GDDR6X의 7개의 연속적인 GDDR 세대가 있다.

PSRAM(유사 정적 램)은 내장된 리프레시 및 주소 제어 회로를 갖춘 동적 램으로, 정적 램(SRAM)과 유사하게 작동한다. DRAM의 높은 집적도와 진정한 SRAM의 사용 편의성을 결합했다. PSRAM은 애플 아이폰(Apple iPhone) 및 XFlar 플랫폼과 같은 기타 임베디드 시스템에 사용된다.[65]

RLDRAM(감소된 레이턴시 디램)은 높은 대역너비와 더불어 속도가 빠른, 랜덤 액세스를 제공하는 DDR SDRAM이다. RLDRAM은 주로 네트워크 응용 프로그램이나 캐시 응용 프로그램에 쓰일 것을 염두에 두고 설계되었다.

4. 작동 원리

DRAM의 작동 원리는 메모리 셀의 커패시터에 전하를 저장하여 데이터를 저장하고, 읽기/쓰기 동작을 통해 데이터를 처리하며, 주기적인 리프레시를 통해 데이터 손실을 방지하는 방식으로 이루어진다.

읽기 동작1. 비트라인 사전 충전: 비트라인은 높은 전압과 낮은 전압의 중간 값으로 미리 충전된다.[29]

2. 워드라인 활성화: 읽고자 하는 행의 워드라인이 활성화되면 해당 셀의 트랜지스터가 켜져 커패시터의 전하가 비트라인으로 이동한다. 이때 커패시터에 저장된 값에 따라 비트라인 전압이 약간 변한다.[29]

3. 감지 증폭기 활성화: 감지 증폭기는 비트라인 쌍 사이의 미세한 전압 차이를 감지하여 증폭한다. 이를 통해 한 비트라인은 최저 전압, 다른 비트라인은 최대 전압에 도달한다.[29]

4. 데이터 출력: 감지 증폭기의 출력은 래치에 저장되고, 열 주소를 통해 외부로 전달된다. 같은 행의 다른 열들은 이미 데이터가 감지되어 래치되었기 때문에 빠르게 읽을 수 있다.[29]

5. 데이터 복원 (리프레시): 읽기 동작 중에는 커패시터의 전하가 일부 방전되므로, 감지 증폭기에서 비트라인으로 전류를 다시 흘려보내 커패시터를 원래 상태로 충전하여 데이터를 보존한다.[29]

쓰기 동작1. 비트라인 설정: 쓰려는 데이터 값에 따라 비트라인에 높은 전압(논리 1) 또는 낮은 전압(논리 0)을 가한다.

2. 워드라인 활성화: 해당 행의 워드라인을 활성화하여 트랜지스터를 켠다.

3. 커패시터 충전/방전: 비트라인의 전압에 따라 커패시터가 충전(논리 1)되거나 방전(논리 0)된다.

4. 데이터 복원(리프레시): 쓰기 동작 후에도 읽기와 마찬가지로 리프레시가 필요하다.

읽기/쓰기 동작 후에는 워드라인을 끄고, 감지 증폭기를 끈 후 비트라인을 다시 사전 충전한다.[29]

리프레시DRAM은 각 셀 내의 커패시터에서 발생하는 전하 누설을 보상하기 위해 주기적으로 데이터를 다시 쓰는 동작, 즉 리프레시가 필요하다. JEDEC 표준에 따라 각 행은 64ms 이하마다 리프레시되어야 한다.[29]

리프레시 방법은 다음과 같다.

대표적인 리프레시 방법으로는 집중 리프레시(규정된 시간마다 모든 행을 한 번에 리프레시)와 분산 리프레시(규정된 시간을 행의 개수로 나눈 주기로 한 행씩 리프레시)가 있다.

4. 1. 메모리 셀 구조

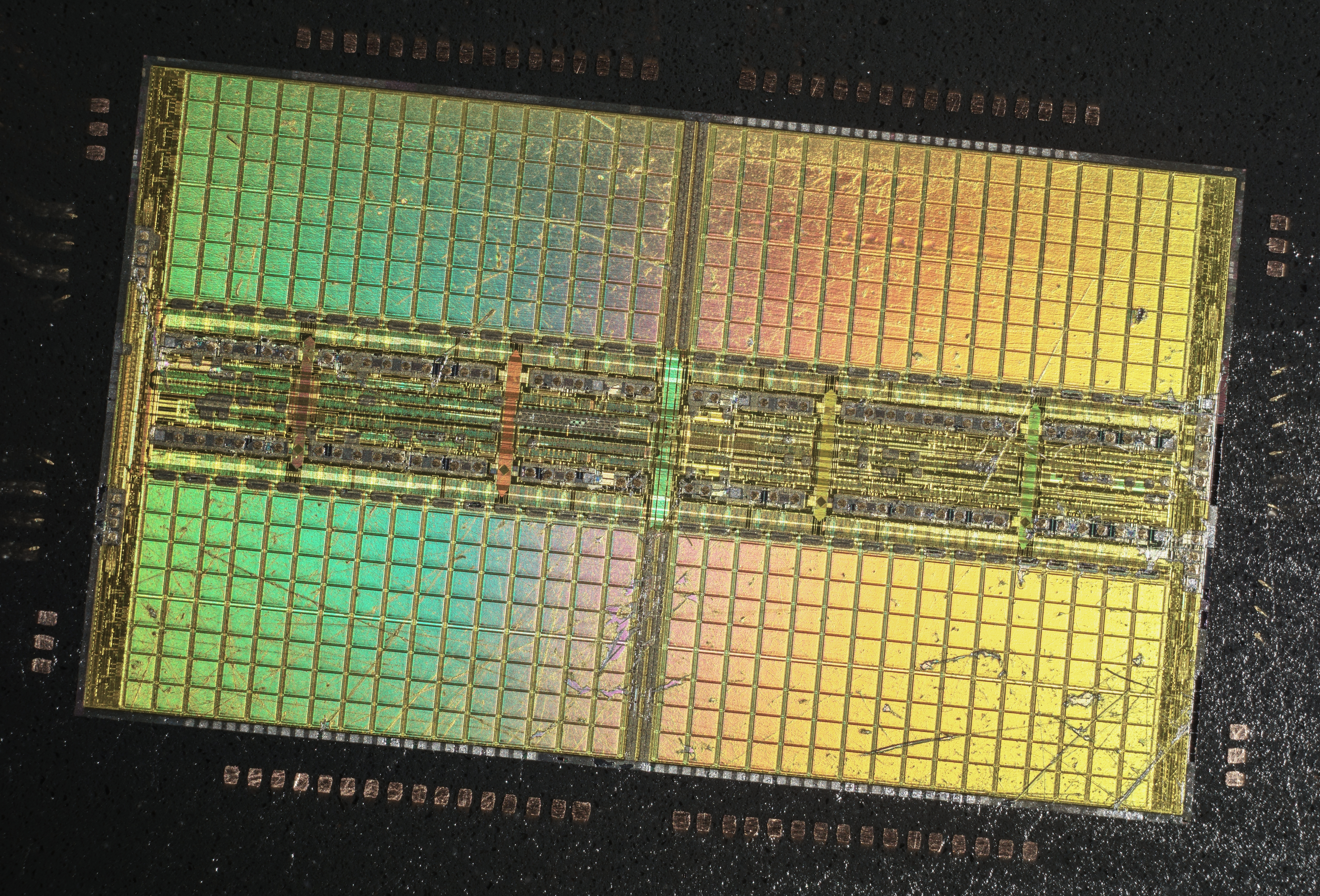

DRAM의 각 데이터 비트는 커패시터 구조에 양전하 또는 음전하로 저장된다. 커패시턴스를 제공하는 구조와 이에 대한 접근을 제어하는 트랜지스터를 통칭하여 ''DRAM 셀''이라고 한다. 이들은 DRAM 어레이의 기본적인 구성 요소이다. 여러 DRAM 메모리 셀 변형이 존재하지만, 현대 DRAM에서 가장 일반적으로 사용되는 변형은 1개의 트랜지스터와 1개의 커패시터(1T1C) 셀이다. 트랜지스터는 쓰기 시 커패시터에 전류를 유입시키고 읽기 시 커패시터를 방전시키는 데 사용된다. 액세스 트랜지스터는 구동 강도를 최대화하고 트랜지스터 간 누설을 최소화하도록 설계되었다.[34]커패시터는 두 개의 단자를 가지고 있으며, 그 중 하나는 액세스 트랜지스터에 연결되고 다른 하나는 접지 또는 VCC/2에 연결된다. 현대 DRAM에서는 후자가 더 일반적인데, 이는 더 빠른 작동을 가능하게 하기 때문이다. 현대 DRAM에서 논리 1을 저장하려면 커패시터에 +VCC/2의 전압이 필요하고, 논리 0을 저장하려면 커패시터에 -VCC/2의 전압이 필요하다. 결과적인 전하는 이며, 여기서 ''Q''는 쿨롬 단위의 전하이고 ''C''는 패럿 단위의 정전 용량이다.[34]

논리 1을 읽거나 쓰려면 워드라인이 VCC와 액세스 트랜지스터의 문턱 전압(VTH)의 합보다 큰 전압으로 구동되어야 한다. 이 전압을 ''VCC 펌핑''(VCCP)이라고 한다. 따라서 커패시터를 방전하는 데 필요한 시간은 커패시터에 저장된 논리 값에 따라 달라진다. 논리 1을 포함하는 커패시터는 액세스 트랜지스터의 게이트 단자 전압이 VCCP보다 높을 때 방전을 시작한다. 커패시터가 논리 0을 포함하는 경우, 게이트 단자 전압이 VTH보다 높을 때 방전을 시작한다.[35]

1990년대 후반부터 1트랜지스터, 제로 커패시터(1T, 또는 1T0C) DRAM 셀은 연구 주제가 되어 왔다. ''1T DRAM''은 기본적인 DRAM 메모리 셀을 구성하는 또 다른 방식으로, 1970년대에 3T 및 4T DRAM을 대체한 고전적인 1트랜지스터/1커패시터(1T/1C) DRAM 셀과는 다르며, 이 또한 때때로 ''1T DRAM''으로 언급되기도 한다.

1T DRAM 셀에서 데이터 비트는 여전히 트랜지스터에 의해 제어되는 용량성 영역에 저장되지만, 이 커패시턴스는 더 이상 별도의 커패시터에 의해 제공되지 않는다. 1T DRAM은 절연체 위에 실리콘(SOI) 트랜지스터에 내재된 기생 바디 커패시턴스를 사용하여 데이터를 저장하는 "커패시터리스" 비트 셀 디자인이다. 로직 설계에서 성가신 것으로 여겨지지만, 이 플로팅 바디 효과는 데이터 저장을 위해 사용될 수 있다. 이는 1T DRAM 셀에 최고의 집적도를 제공할 뿐만 아니라, 동일한 SOI 공정 기술로 구성되어 고성능 로직 회로와의 쉬운 통합을 가능하게 한다.[36]

셀의 리프레시는 여전히 필요하지만, 1T1C DRAM과 달리 1T DRAM에서의 읽기는 파괴적이지 않다. 저장된 전하는 트랜지스터의 임계 전압에서 감지 가능한 변화를 유발한다.[37] 성능 면에서는, 접근 시간은 커패시터 기반 DRAM보다 훨씬 뛰어나지만, SRAM보다는 약간 떨어진다. 1T DRAM에는 여러 종류가 있는데, 혁신적인 실리콘(Innovative Silicon)의 상용화된 Z-RAM, 르네사스(Renesas)의 TTRAM[38], 그리고 UGR/CNRS 컨소시엄의 A-RAM이 있다.

DRAM의 내부 회로는 각 1개씩의 캐패시터와 전계 효과 트랜지스터(FET)로 구성된 "메모리 셀" 부분과, 다수의 메모리 셀이 배열된 매트릭스 주위를 둘러싼 "주변 회로"로 구성된다.

DRAM의 집적도를 높이기 위해서는 메모리 셀을 가능한 작게 만드는 것이 유효하다. 따라서 캐패시터와 FET를 좁은 공간에 채워 넣기 위해 다양한 궁리가 이루어지고 있다.

각 메모리 셀은 캐패시터 1개와 스위치용 FET 1개로 구성된다. 기억 셀은 바둑판 모양으로 배열되어 있고, 가로 방향과 세로 방향으로 워드선과 비트선이 뻗어 있다. 기억 데이터는 메모리 셀의 캐패시터에 전하가 있는 경우는 논리 "1", 없는 경우는 논리 "0"으로 취급되며, 하나의 메모리 셀에서 1비트의 기억을 유지한다.[71]

4. 2. 읽기/쓰기 동작

DRAM의 각 비트는 커패시터에 양(+) 또는 음(-) 전하 형태로 저장된다. 읽기 또는 쓰기를 하려면 워드라인을 활성화하여 액세스 트랜지스터를 켠다. 이 트랜지스터는 커패시터와 비트라인을 연결한다.[29]읽기 동작1. 비트라인 사전 충전: 비트라인은 높은 전압과 낮은 전압의 중간 값(예: 0V와 1V 사이의 0.5V)으로 사전 충전된다.[29]

2. 워드라인 활성화: 읽고 싶은 행의 워드라인이 활성화되면, 해당 셀의 트랜지스터가 켜지면서 커패시터의 전하가 비트라인으로 이동한다. 커패시터에 저장된 값에 따라 비트라인 전압은 약간 증가하거나 감소한다.[29]

3. 감지 증폭기 활성화: 감지 증폭기는 비트라인 쌍 사이의 작은 전압 차이를 감지하고 증폭한다. 한 비트라인은 최저 전압, 다른 비트라인은 최대 전압에 도달하게 된다.[29]

4. 데이터 출력: 감지 증폭기의 출력은 래치에 저장되고, 열 주소를 통해 외부로 전달된다. 같은 행의 다른 열들은 이미 데이터가 감지되어 래치되었기 때문에 빠르게 읽을 수 있다.[29]

5. 데이터 복원 (리프레시): 읽기 동작 중에는 커패시터의 전하가 일부 방전되므로, 감지 증폭기에서 비트라인으로 전류를 다시 흘려보내 커패시터를 원래 상태로 충전한다. 이를 통해 데이터가 보존된다(새로 고침).[29]

쓰기 동작1. 비트라인 설정: 쓰려는 데이터 값에 따라 비트라인에 높은 전압(논리 1) 또는 낮은 전압(논리 0)을 가한다.

2. 워드라인 활성화: 해당 행의 워드라인을 활성화하여 트랜지스터를 켠다.

3. 커패시터 충전/방전: 비트라인의 전압에 따라 커패시터가 충전(논리 1)되거나 방전(논리 0)된다.

4. 데이터 복원(리프레시): 쓰기 동작 후에도 읽기와 마찬가지로 리프레시가 필요하다.

읽기/쓰기 동작 후에는 워드라인을 끄고, 감지 증폭기를 끈 후 비트라인을 다시 사전 충전한다.[29]

4. 3. 리프레시

동적 램(DRAM)은 데이터를 저장하는 각 셀 내의 커패시터에 전하가 누설되는 것을 보상하기 위해 주기적으로 데이터를 다시 쓰는 동작, 즉 리프레시가 필요하다.일반적으로 제조업체는 JEDEC 표준에 따라 각 행을 64ms 이하마다 리프레시해야 한다고 명시한다.[29]

리프레시를 수행할 행 주소를 지정하는 방법은 다음과 같다.

대표적인 리프레시 방법은 다음과 같다.

- 집중 리프레시: 규정된 시간마다 소자 내의 모든 행을 한 번에 리프레시한다.

- 분산 리프레시: 규정된 시간을 행의 개수로 나눈 주기로 한 행씩 리프레시한다.

일부 시스템은 64ms마다 모든 행을 포함하는 일련의 활동으로 각 행을 리프레시하는 반면, 다른 시스템은 64ms 간격 동안 한 번에 한 행씩 리프레시한다. 예를 들어 8,192개(213)의 행이 있는 시스템은 7.8 μs(64 ms / 8,192 행)마다 한 행씩 분산된 재생률이 필요하다. 일부 실시간 시스템은 비디오 장비에서 10~20 ms마다 발생하는 수직 블랭킹 간격과 같이 시스템의 나머지 작동을 제어하는 외부 타이머 기능에 의해 결정된 메모리의 일부를 한 번에 리프레시한다.

일부 조건에서는 DRAM이 몇 분 동안 리프레시되지 않았더라도 DRAM의 대부분의 데이터를 복구할 수 있다.[30]

5. 구조

DRAM의 내부 회로는 각 1개씩의 캐패시터와 전계 효과 트랜지스터(FET)로 구성된 "메모리 셀" 부분과, 다수의 메모리 셀이 배열된 매트릭스 주위를 둘러싼 "주변 회로"로 구성된다.[71] DRAM의 집적도를 높이기 위해서는 메모리 셀을 가능한 작게 만드는 것이 중요하다. 따라서 좁은 공간에 캐패시터와 FET를 배치하기 위해 다양한 기술이 사용되고 있다.

각 메모리 셀은 캐패시터 1개와 스위치용 FET 1개로 구성된다. 기억 셀은 바둑판 모양으로 배열되어 있고, 가로 방향과 세로 방향으로 워드선과 비트선이 뻗어 있다. 기억 데이터는 메모리 셀의 캐패시터에 전하가 있는 경우는 논리 "1", 없는 경우는 논리 "0"으로 취급되며, 하나의 메모리 셀에서 1비트의 기억을 유지한다.[71]

메모리 셀에 축적된 전하는 소자 내부의 누설 전류에 의해 서서히 손실되어, 전하가 없는 상태와의 구별이 어려워진다. 그래서 정기적으로 전하를 보충하는 조작이 필요하다. 이 조작을 '''리프레시'''라고 부른다. 리프레시는 1행 단위로 동시에 접근하여 실행되며, 규정된 시간(수십 밀리 초 정도) 안에 소자 내의 모든 행에 대해 실행해야 한다. 리프레시라는 용어는 미국 인텔사에 의해 붙여졌으며, 콘덴서 메모리의 원조인 ABC에서는 조깅이라고 불렸다.[76]

5. 1. 메모리 셀 어레이

DRAM 셀은 워드라인과 비트라인을 통해 제어하고 접근하기 쉽도록 규칙적인 직사각형 격자 패턴으로 배열된다. 배열에서 DRAM 셀의 물리적 레이아웃은 일반적으로 열에서 인접한 두 DRAM 셀이 단일 비트라인 접점을 공유하여 면적을 줄이도록 설계된다. DRAM 셀 면적은 ''n''F2로 주어지며, 여기서 ''n''은 DRAM 셀 설계에서 파생된 숫자이고 ''F''는 주어진 공정 기술의 최소 피처 크기이다. 이 방식은 DRAM 셀 면적이 피처 크기에 따라 선형 또는 거의 선형적인 속도로 확장되므로 다양한 공정 기술 세대에 걸쳐 DRAM 크기를 비교할 수 있게 해준다. 현대 DRAM 셀의 일반적인 면적은 6–8 F2 사이이다.수평 와이어인 워드라인은 해당 행의 모든 접근 트랜지스터의 게이트 터미널에 연결된다. 수직 비트라인은 해당 열의 트랜지스터 소스 터미널에 연결된다. 워드라인과 비트라인의 길이는 제한되어 있다. 워드라인 길이는 배열의 원하는 성능에 의해 제한되는데, 워드라인을 가로질러야 하는 신호의 전파 시간은 RC 시정수에 의해 결정되기 때문이다. 비트라인 길이는 그 정전 용량(길이에 따라 증가)에 의해 제한되며, 적절한 감지를 위해 범위를 유지해야 한다(DRAM은 비트라인에 방전된 커패시터의 전하를 감지하여 작동하므로). 비트라인 길이는 또한 DRAM이 소비할 수 있는 작동 전류량과 전력 소모 방식에 의해 제한되는데, 이 두 가지 특성이 비트라인의 충전 및 방전에 의해 크게 결정되기 때문이다.[39]

DRAM의 내부 회로는 각 1개씩의 캐패시터와 전계 효과 트랜지스터(FET)로 구성된 "메모리 셀" 부분과, 다수의 메모리 셀이 배열된 매트릭스 주위를 둘러싼 "주변 회로"로 구성된다. DRAM의 집적도를 높이기 위해서는 메모리 셀을 가능한 작게 만드는 것이 유효하다. 따라서 캐패시터와 FET를 좁은 공간에 채워 넣기 위해 다양한 궁리가 이루어지고 있다.

각 메모리 셀은 캐패시터 1개와 스위치용 FET 1개로 구성된다. 기억 셀은 바둑판 모양으로 배열되어 있고, 가로 방향과 세로 방향으로 워드선과 비트선이 뻗어 있다. 기억 데이터는 메모리 셀의 캐패시터에 전하가 있는 경우는 논리 "1", 없는 경우는 논리 "0"으로 취급되며, 하나의 메모리 셀에서 1비트의 기억을 유지한다.[71]

메모리 셀에 축적된 전하는 소자 내부의 누설 전류에 의해 서서히 손실되어, 전하가 없는 상태와의 구별이 어려워진다. 그래서 정기적으로 전하를 보충하는 조작이 필요하게 된다. 이 조작을 '''리프레시'''라고 부른다. 리프레시는 1행 단위로 동시에 액세스함으로써 실시되며, 규정된 시간 내(수십 밀리 초 정도)에 소자 내의 모든 행에 대해 행해야 한다. 리프레시라는 용어는 미국 인텔사에 의해 붙여졌으며, 콘덴서 메모리의 원조인 ABC에서는 조깅이라고 불렸다.[76]

5. 2. 주변 회로

DRAM의 내부 회로는 각 1개씩의 캐패시터와 FET로 구성된 "메모리 셀" 부분과, 다수의 메모리 셀이 배열된 매트릭스 주위를 둘러싼 "주변 회로"로 구성된다.[71] DRAM의 집적도를 높이기 위해서는 메모리 셀을 가능한 작게 만드는 것이 중요하다. 따라서 좁은 공간에 캐패시터와 FET를 배치하기 위해 다양한 기술이 사용되고 있다.5. 3. 어레이 구조

개방형 비트 라인 어레이는 1세대(1 Kbit) DRAM IC부터 64 Kbit 세대(및 일부 256 Kbit 세대 장치)까지 사용되었다. 이 구조에서는 비트 라인이 여러 세그먼트로 나뉘고, 차동 감지 증폭기가 비트 라인 세그먼트 사이에 배치된다. 감지 증폭기가 비트 라인 세그먼트 사이에 있어 출력을 어레이 외부로 라우팅하려면 워드 라인과 비트 라인을 구성하는 데 사용되는 추가적인 상호 연결 계층이 필요하다. 어레이 가장자리에 있는 DRAM 셀에는 인접한 세그먼트가 없기 때문에 더미 비트 라인 세그먼트가 제공된다. 개방형 비트 라인 어레이는 작은 면적을 가지지만, 더미 비트 라인 세그먼트로 인해 이 장점이 কিছুটা 감소한다. 또한, 노이즈에 취약하여 차동 감지 증폭기의 효율성에 영향을 미친다. 각 비트 라인 세그먼트는 다른 비트 라인 세그먼트와 공간적 관계가 없으므로 노이즈가 두 비트 라인 세그먼트 중 하나에만 영향을 미칠 가능성이 높다.[71]접힌 비트 라인 배열은 비트 라인을 쌍으로 배열하여 공통 모드 노이즈 제거 특성이 우수하다. 1980년대 중반 256 Kbit 세대부터 DRAM IC에 나타나기 시작하여 현대 DRAM IC에서 주로 사용된다. 회로도 관점에서 개방형 배열 구조를 기반으로 하기 때문에 "접힌"이라고 불린다. 열에서 DRAM 셀을 교대로 쌍으로 제거하고(두 개의 DRAM 셀이 단일 비트 라인 접점을 공유하기 때문) 인접한 열의 DRAM 셀을 빈 공간으로 이동하는 것처럼 보인다.

비트 라인이 꼬이는 위치는 추가적인 면적을 차지한다. 면적 오버헤드를 최소화하기 위해 노이즈를 줄일 수 있는 가장 간단하고 면적을 최소화하는 꼬임 방식을 선택한다. 공정 기술이 향상되어 최소 피쳐 크기가 줄어들면서 인접한 금속 와이어 간의 결합이 피치에 반비례하여 신호 대 잡음 문제가 악화된다. 따라서 사용되는 배열 접힘 및 비트 라인 꼬임 방식은 복잡성을 증가시켜야 한다. 면적에 미치는 영향을 최소화하면서 바람직한 노이즈 내성 특성을 갖는 방식은 현재 연구 주제이다.[71]

공정 기술의 발전은 개방형 비트 라인 배열 구조가 장기적인 면적 효율성 측면에서 더 나은 이점을 제공할 수 있다면 선호될 수 있다. 접힌 배열 구조는 공정 기술의 발전에 맞춰 점점 더 복잡한 접기 방식을 필요로 하기 때문이다. 공정 기술, 배열 구조 및 면적 효율성 간의 관계는 활발하게 연구되는 분야이다.

21세기 이후에는 고집적화를 위해 오픈 비트선이 사용되게 되었다. 종래 방식에서는 본래의 비트선에 평행하게 왕복 비트선이 배선되어 노이즈의 영향을 줄였다. 그러나 셀이 작아지고 전극 재료로 폴리실리콘 대신 금속 재료를 사용하면서 기생 저항과 읽기 저항이 감소하여 읽기 전류를 많이 얻을 수 있게 되었다. 이에 따라 미세화 및 고집적화 요구에 맞춰 왕복 비트선 방식 대신 오픈 비트선 방식이 도입되었다.[76]

6. 오류 감지 및 정정

컴퓨터 시스템 내부의 전기적 또는 자기적 간섭은 DRAM의 단일 비트가 자발적으로 반전되도록 할 수 있다. DRAM 칩에서 발생하는 대부분의 일회성("소프트") 오류는 주로 우주 방사선에서 발생하는 중성자와 같은 배경 방사선의 결과로 발생하며, 이로 인해 하나 이상의 메모리 셀 내용이 변경되거나 이를 읽고 쓰는 데 사용되는 회로에 간섭이 발생할 수 있다.[40]

이 문제는 중복 메모리 비트와 이러한 비트를 사용하여 소프트 오류를 감지하고 수정하는 추가 회로를 사용하여 완화할 수 있다. 대부분의 경우 감지 및 수정은 메모리 컨트롤러에서 수행된다. 때로는 필요한 로직이 DRAM 칩 또는 모듈 내에서 투명하게 구현되어 그렇지 않으면 ECC를 사용할 수 없는 시스템에 대해 ECC 메모리 기능을 사용할 수 있게 한다.[40] 추가 메모리 비트는 패리티를 기록하고 오류 정정 코드 (ECC)를 사용하여 누락된 데이터를 재구성할 수 있도록 하는 데 사용된다. 패리티를 사용하면 모든 단일 비트 오류(실제로는 잘못된 비트의 모든 홀수 개수)를 감지할 수 있다. 가장 일반적인 오류 정정 코드인 SECDED 해밍 코드를 사용하면 단일 비트 오류를 수정할 수 있으며, 일반적인 구성에서는 추가 패리티 비트를 사용하여 이중 비트 오류를 감지할 수 있다.[41]

최근 연구에 따르면 오류율 범위가 7자릿수 이상 차이가 나는 매우 다양한 오류율이 나타났으며, 이는 대략 시간당 기가바이트당 한 비트 오류에서 기가바이트당 세기에 한 비트 오류에 해당한다.[42][43][44] 2009년 Schroeder et al. 연구에 따르면 연구 대상 컴퓨터가 1년에 최소한 한 번의 수정 가능한 오류를 겪을 확률이 32%였으며, 이러한 오류의 대부분은 소프트 오류가 아닌 간헐적인 하드 오류이며, 칩 포장에 들어간 미량의 방사성 물질이 알파 입자를 방출하여 데이터를 손상시킨다는 증거를 제시했다.[45]

정보는 각 메모리 셀의 캐패시터 전하 형태로 저장되지만, 우주선 등 방사선이 캐패시터에 조사되면 전하가 손실되어 데이터가 변경되는 현상이 발생한다. 이것은 Soft error|소프트 에러영어라고 불리며, 고에너지 방사선을 항상 받을 가능성이 있는 우주 항공 분야뿐만 아니라, 지상의 일상적인 환경에서도 발생할 수 있으며, 메모리를 가진 기기의 우발적인 이상 동작의 원인이 된다.

ECC 메모리에서 중요한 점은, 여분의 비트에 오류 정정 부호를 기록하여, Soft error|소프트 에러영어에 의한 데이터 손상을 감지하고 수정할 수 있다는 것이다. 고신뢰성이 요구되는 서버 등에서 사용된다.

7. 보안 문제

동적 램은 전원이 공급되고 짧은 시간(보통 64ms)마다 새로 고쳐질 때만 내용을 유지하도록 보장되지만, 메모리 셀의 캐패시터는 특히 저온에서 오랫동안 값을 유지하는 경우가 많다.[49] 어떤 조건에서는 DRAM의 대부분의 데이터가 몇 분 동안 새로 고쳐지지 않아도 복구될 수 있다.[48] 이러한 특성을 이용하여 보안을 우회하고, 전원이 꺼지면 파괴되는 것으로 간주되는 메인 메모리에 저장된 데이터를 복구할 수 있다.

데이터 잔류를 이용한 공격 방법은 다음과 같다.

- 컴퓨터를 빠르게 재부팅하여 메인 메모리의 내용을 읽어낸다.

- 컴퓨터의 메모리 모듈을 제거하고 냉각하여 데이터 잔류를 연장한 다음 다른 컴퓨터로 전송하여 읽어낸다.

이러한 공격은 오픈 소스 TrueCrypt, 마이크로소프트의 BitLocker 드라이브 암호화, 애플의 FileVault와 같은 인기 있는 디스크 암호화 시스템을 우회하는 것으로 시연되었다.[49] 이러한 유형의 공격은 콜드 부팅 공격이라고 불린다.

동적 메모리는 주기적인 새로 고침(refresh)이 필요하며, 동적 메모리를 읽는 것은 파괴적인 작업이어서 읽은 행의 기억 셀을 다시 충전해야 한다. 이 과정이 완벽하지 않으면 읽기 작업으로 인해 소프트 에러가 발생할 수 있다. 특히, 근처 셀 사이에 약간의 전하가 새어 나가 한 행의 새로 고침 또는 읽기로 인해 인접하거나 심지어 근처 행에서 '방해 오류'가 발생할 위험이 있다. 방해 오류에 대한 인식은 1970년대 초 최초의 상용 DRAM(인텔 1103)까지 거슬러 올라간다. 제조업체의 완화 기술에도 불구하고, 2014년 분석에서 2012년과 2013년에 제조된 상용 DDR3 DRAM 칩이 방해 오류에 취약하다는 것이 밝혀졌다.[50] 관찰된 비트 반전을 일으키는 관련 부작용은 로우 해머라고 불린다.

7. 1. 데이터 잔류

동적 메모리는 전원이 공급되고 짧은 시간(보통 64ms)마다 새로 고쳐질 때만 내용을 유지하도록 ''보장''되지만, 메모리 셀의 캐패시터는 특히 저온에서 훨씬 더 오랫동안 값을 유지하는 경우가 많다.[49] 어떤 조건에서는 DRAM의 대부분의 데이터가 몇 분 동안 새로 고쳐지지 않아도 복구될 수 있다.[48]이러한 특성은 보안을 우회하고 전원 끄기 시 파괴된 것으로 간주되는 메인 메모리에 저장된 데이터를 복구하는 데 사용될 수 있다. 컴퓨터를 빠르게 재부팅하고 메인 메모리의 내용을 읽어내거나, 컴퓨터의 메모리 모듈을 제거하고 냉각하여 데이터 잔류를 연장한 다음 다른 컴퓨터로 전송하여 읽어낼 수 있다. 이러한 공격은 오픈 소스 TrueCrypt, 마이크로소프트의 BitLocker 드라이브 암호화, 애플의 FileVault와 같은 인기 있는 디스크 암호화 시스템을 우회하는 것으로 시연되었다.[49] 컴퓨터에 대한 이러한 유형의 공격은 종종 콜드 부팅 공격이라고 불린다.

7. 2. 메모리 손상

동적 메모리는 그 특성상 주기적인 새로 고침(refresh)이 필요하다. 또한 동적 메모리를 읽는 것은 파괴적인 작업이어서, 읽은 행의 기억 셀을 다시 충전해야 한다. 이러한 과정이 완벽하지 않으면 읽기 작업으로 인해 소프트 에러가 발생할 수 있다. 특히, 근처 셀 사이에 약간의 전하가 새어 나가 한 행의 새로 고침 또는 읽기로 인해 인접하거나 심지어 근처 행에서 '방해 오류'가 발생할 위험이 있다. 방해 오류에 대한 인식은 1970년대 초 최초의 상용 DRAM(인텔 1103)까지 거슬러 올라간다. 제조업체에서 사용하는 완화 기술에도 불구하고, 상업 연구원들은 2014년 분석에서 2012년과 2013년에 제조된 상용 DDR3 DRAM 칩이 방해 오류에 취약하다는 것을 증명했다.[50] 관찰된 비트 반전을 일으키는 관련 부작용은 로우 해머라고 불린다.8. 한국 DRAM 산업

2000년대 중반, 삼성전자와 SK하이닉스는 Qimonda, 엘피다, Micron와 함께 DRAM 시장을 과점했다. 그러나 2008년 세계 금융 위기 등의 영향으로 DRAM 가격이 폭락하면서[80], 2009년 독일 키몬다가 파산하는 등[83] 업계에 큰 변화가 일어났다.

키몬다 파산 이후, 대만 기업들은 범용 D램에서 철수하거나 대기업에 흡수되었고, 일본 엘피다 메모리 역시 2012년 파산하여 2013년 마이크론에 인수되었다. 2013년에는 삼성전자, 마이크론, SK하이닉스의 3강 체제가 구축되었다. SK하이닉스는 엘피다 파산 후인 2013년 2분기에 영업이익 10억원을 넘어서면서 치킨 게임이 종료되었다고 평가받았다.

8. 1. 발전 과정

1970년대 이후 메모리 반도체 제조 업계는 기술적 차별화가 적어, 선도 업체들이 반도체 제조 장치 업체와 협력하여 생산 공장을 정비해왔다. 이 과정에서 제조 장치 업체는 추종 업체에게 장비를 판매하여 이익을 얻고, 추종 업체는 높은 생산성을 위한 경험을 축적하는 방식으로 차별화를 꾀했다.1990년대 중반 이후, DRAM 제조사들은 과거의 실패를 바탕으로 수요 예측에 신중을 기하며 설비 투자를 진행하고, 가격 조작 및 공급 관리를 통해 실리콘 사이클을 방지하고자 노력했다.

2000년대 중반에는 삼성전자, SK하이닉스, Qimonda, 엘피다, Micron의 5개 주요 회사가 업계를 과점했다. 2007년, Windows Vista 출시를 앞두고 각 회사는 PC 수요 확대를 예측하여 생산량을 늘렸으나, 이는 수요와 공급의 불균형을 초래하여 DRAM 가격이 폭락하는 실리콘 사이클을 발생시켰다.[80]

2008년에는 DRAM 최대 업체인 삼성을 제외한 다른 회사들은 큰 적자를 기록했고[81][82], 2009년에는 독일 키몬다사가 파산했다.[83] 이후에도 DRAM 가격 하락은 계속되었고, 삼성은 2011년에 유일하게 흑자를 기록했지만, 주요 업체들은 시장 점유율 확보를 위해 적자를 감수하며 DRAM을 계속 생산하는 치킨 게임 상황에 놓였다.

키몬다의 파산 이후, 대기업에 의한 시장 과점 현상이 심화되었고, 2009년부터 2013년경까지 D램 업계의 세계적인 재편이 이루어졌다. Nanya를 비롯한 대만 업체들은 범용 D램에서 철수하거나 대기업에 흡수되었다.

엘피다는 2012년 파산하여 2013년 마이크론의 자회사가 되었고, 이로 인해 마이크론은 업계 2위로 올라섰다. 2013년에는 업계가 삼성전자, 마이크론, SK하이닉스의 3강 체제로 재편되었고, SK하이닉스는 2013년 2분기에 영업이익 1조 원을 넘어서며 치킨 게임이 종료되었다고 평가받았다.

8. 2. 시장 점유율

2000년대 중반에는 삼성전자, SK하이닉스, Qimonda, 엘피다, Micron의 5개 주요 회사가 업계를 과점했다. 그러나 2009년 1월 23일, 독일 키몬다가 파산하면서[83] 업계에 큰 변화가 생겼다. 이후, 대만 회사들은 범용 D램에서 철수하거나 대기업에 흡수되었고, 엘피다 또한 2012년 2월에 파산하여 2013년 7월에 마이크론에 인수되었다.이러한 과정을 거쳐, 2013년에는 DRAM 시장은 삼성전자, 마이크론, SK하이닉스의 3강 체제로 재편되었다. 2023년 현재 삼성전자와 SK하이닉스는 전 세계 DRAM 시장의 70% 이상을 점유하고 있다.

8. 3. 기술 리더십

2000년대 중반에는 삼성전자, SK하이닉스 등 한국 기업들을 포함, 키몬다, 엘피다 메모리, 마이크론 테크놀로지 5개 회사가 DRAM 시장을 과점하고 있었다.[80] 그러나 2008년 세계 금융 위기 등의 영향으로 DRAM 가격이 폭락하면서, 2009년 독일 키몬다가 파산하는 등 업계 재편이 이루어졌다.[83]키몬다 파산 이후, 대만 기업들은 범용 D램에서 철수하거나 대기업에 흡수되었고, 일본 엘피다 메모리 역시 2012년 파산하여 2013년 마이크론에 인수되었다. 이러한 과정을 거쳐 2013년에는 삼성전자, 마이크론, SK하이닉스의 3강 체제가 구축되었다.

특히, 삼성전자는 EUV(Extreme Ultraviolet) 노광 장비를 활용한 미세 공정 기술에서 앞서나가며 기술 리더십을 확보하고 있다. 한국 기업들은 DDR5, HBM 등 차세대 DRAM 기술 개발을 주도하고 있다.

8. 4. 과제 및 전망

메모리 반도체 제조 업계는 1970년대 이후 기술적 차별화가 적은 편이다. 선도 업체들은 반도체 제조 장치 업체와 협력하여 최첨단 기술을 도입하고, 공동 개발한 장치를 저렴하게 조달받는다. 후발 업체들은 독자 기술 개발보다는 생산성 향상에 집중한다.과거에는 "실리콘 사이클"이라 불리는 경기 순환이 반도체 업계에 큰 영향을 미쳤다. PC 수요 확대에 따라 메모리 가격이 상승하면, 제조사들은 생산 설비를 확대한다. 그러나 생산량이 증가할 무렵에는 수요가 감소하여 가격이 폭락하는 현상이 반복되었다. 이로 인해 많은 기업들이 반도체 사업에서 철수했다.

2000년대 중반에는 삼성, SK하이닉스, Qimonda, 엘피다, Micron의 5개 회사가 시장을 과점했다. 2007년, Windows Vista 출시로 PC 수요가 증가할 것으로 예상하고 생산량을 늘렸으나, 예상 밖의 판매 부진과 미국 발 금융 위기 등으로 인해 DRAM 가격이 폭락했다.[80]

DRAM 가격은 2007년 한 해 동안 80% 정도 하락하여, 대부분의 제조사가 큰 적자를 기록했다.[81][82] 2009년에는 독일 키몬다사가 파산했다.[83]

2009년 이후에도 DRAM 가격 하락은 계속되었고, 주요 업체들은 시장 점유율 확보를 위해 치킨 게임을 벌였다. 키몬다의 파산 이후, 대기업에 의한 과점 현상이 심화되었고, 2009년부터 2013년경까지 D램 업계의 세계적인 재편이 이루어졌다.

Nanya는 2012년에 범용 D램에서 철수했고, ProMOS는 글로벌파운드리에 인수되었다. 엘피다는 2012년에 파산하여 2013년에 마이크론에 인수되었다. 마이크론은 엘피다 인수를 통해 업계 2위로 올라섰다.

2013년에는 삼성전자, 마이크론, SK하이닉스의 3강 체제가 구축되었다. SK하이닉스는 2013년 2분기에 영업이익 1조 원을 넘어서며 치킨 게임이 종료되었다고 평가받았다.

참조

[1]

웹사이트

How to "open" microchip and what's inside? : ZeptoBars

http://zeptobars.com[...]

2012-11-15

[2]

웹사이트

NeXTServiceManualPages1-160

http://www.nextcompu[...]

[3]

웹사이트

Are the Major DRAM Suppliers Stunting DRAM Demand?

[4]

웹사이트

DRAM Boom and Bust is Business as Usual

https://www.eetimes.[...]

2018-09-20

[5]

서적

Colossus: The secrets of Bletchley Park's code-breaking computers

https://books.google[...]

Oxford University Press

2010

[6]

웹사이트

Spec Sheet for Toshiba "TOSCAL" BC-1411

[7]

간행물

Toscal BC-1411 calculator

http://collection.sc[...]

2017-07-29

[8]

웹사이트

Toshiba "Toscal" BC-1411 Desktop Calculator

http://www.oldcalcul[...]

2007-05-20

[9]

웹사이트

Memory Circuit

https://patents.goog[...]

2023-06-18

[10]

웹사이트

1966: Semiconductor RAMs Serve High-speed Storage Needs

https://www.computer[...]

[11]

웹사이트

DRAM

https://www.ibm.com/[...]

IBM

2017-08-09

[12]

웹사이트

IBM100 — DRAM

https://www.ibm.com/[...]

2017-08-09

[13]

웹사이트

Robert Dennard

https://www.britanni[...]

2023-09

[14]

웹사이트

1970: Semiconductors compete with magnetic cores

https://www.computer[...]

[15]

특허

Field-effect transistor memory

https://patents.goog[...]

[16]

웹사이트

Who Invented the Intel 1103 DRAM Chip?

http://inventors.abo[...]

ThoughtCo

2018-02-23

[17]

웹사이트

Archived copy

http://archive.compu[...]

[18]

웹사이트

Reverse-engineering the classic MK4116 16-kilobit DRAM chip

http://www.righto.co[...]

2020-11

[19]

웹사이트

Oral History of Robert Proebsting

https://www.cs.utexa[...]

Computer History Museum

2005-09-14

[20]

간행물

"Outbreak of Japan-US Semiconductor War"

http://www.shmj.or.j[...]

2020-02-29

[21]

서적

American Industrial Policy: Free or Managed Markets?

https://books.google[...]

Springer

2016

[22]

뉴스

https://www.nytimes.[...]

1987-11-03

[23]

학술지

Electronic Design

https://books.google[...]

Hayden Publishing Company

1993

[24]

웹사이트

KM48SL2000-7 Datasheet

https://www.datashee[...]

Samsung

1992-08

[25]

뉴스

Samsung Electronics Develops First 128Mb SDRAM with DDR/SDR Manufacturing Option

https://www.samsung.[...]

Samsung

1999-02-10

[26]

뉴스

https://phys.org/new[...]

Phys.org

2006

[27]

웹사이트

Lecture 12: DRAM Basics

http://www.eng.utah.[...]

2011-02-17

[28]

웹사이트

Lecture 20: Memory Technology

https://www.cs.princ[...]

2004-11-23

[29]

문서

2007

[30]

간행물

Lest We Remember: Cold Boot Attacks on Encryption Keys

https://www.usenix.o[...]

2015-01-05

[31]

웹사이트

Micron 4 Meg x 4 EDO DRAM data sheet

http://download.micr[...]

[32]

웹사이트

Corsair CMX1024-3200 (1 GByte, two bank unbuffered DDR SDRAM DIMM)

http://www.corsairme[...]

2003-12

[33]

웹사이트

Corsair TWINX1024-3200XL dual-channel memory kit

http://www.corsairme[...]

2004-05

[34]

문서

2007

[35]

문서

2007

[36]

웹사이트

Pro Audio Reference

https://aes2.org/pub[...]

2024-08-08

[37]

간행물

Principles of the 1T Dynamic Access Memory Concept on SOI

http://legwww.epfl.c[...]

2007-10-07

[38]

서적

Proceedings of the IEEE 2005 Custom Integrated Circuits Conference, 2005

2005-09-21

[39]

문서

J. Park et al., IEDM 2015.

[40]

웹사이트

ECC DRAM – Intelligent Memory

http://www.intellige[...]

2015-01-16

[41]

웹사이트

Soft errors' impact on system reliability

http://www.edn.com/a[...]

Cypress Semiconductor

2004-09-30

[42]

문서

Comparison of Accelerated DRAM Soft Error Rates Measured at Component and System Level

Borucki

2008

[43]

문서

"DRAM errors in the wild: a large-scale field study"

http://www.cs.toront[...]

2009

[44]

웹사이트

A Memory Soft Error Measurement on Production Systems

http://www.ece.roche[...]

2018-05-08

[45]

웹사이트

DRAM's Damning Defects—and How They Cripple Computers - IEEE Spectrum

https://spectrum.iee[...]

2015-11-24

[46]

웹사이트

"A Realistic Evaluation of Memory Hardware Errors and Software System Susceptibility". Usenix Annual Tech Conference 2010

http://www.cs.roches[...]

[47]

웹사이트

Cycles, cells and platters: an empirical analysis of hardware failures on a million consumer PCs. Proceedings of the sixth conference on Computer systems (EuroSys '11). pp 343-356

http://research.micr[...]

[48]

저널

Analysis of radiation effects on individual DRAM cells

2000-12

[49]

웹사이트

Center for Information Technology Policy » Lest We Remember: Cold Boot Attacks on Encryption Keys

http://citp.princeto[...]

[50]

웹사이트

Flipping Bits in Memory Without Accessing Them: DRAM Disturbance Errors

http://users.ece.cmu[...]

2015-03-10

[51]

웹사이트

SDRAM Memory Basics & Tutorial

http://www.radio-ele[...]

2018-02-26

[52]

기술보고서

Understanding DRAM Operation

http://www.ece.cmu.e[...]

IBM

1996-12

[53]

기술보고서

Z80 CPU

http://www.zilog.com[...]

[54]

웹사이트

What is DRAM refresh and why is the weird Apple II video memory layout affected by it?

https://retrocomputi[...]

2020-03-03

[55]

기술보고서

Various Methods of DRAM Refresh

http://www.downloads[...]

Micron Technology

[56]

문서

2007

[57]

문서

2007

[58]

서적

Upgrading and Repairing Laptops

https://books.google[...]

Que; Har/Cdr Edition

[59]

기술보고서

EDO (Hyper Page Mode)

https://www.ardent-t[...]

IBM

1996-06-06

[60]

웹사이트

Memory Grades, the Most Confusing Subject

https://simmtester.c[...]

CST, Inc.

2017-11-01

[61]

웹사이트

Bunnie's RAM FAQ

http://www.bunniestu[...]

1996-09-14

[62]

저널

High-Performance DRAMs in Workstation Environments

http://www.bunniestu[...]

2017-11-02

[63]

웹사이트

Burst EDO (BEDO) - Ram Guide {{pipe}} Tom's Hardware

https://www.tomshard[...]

Tomshardware.com

2022-03-09

[64]

웹사이트

Window RAM (WRAM)

http://www.pcguide.c[...]

[65]

뉴스

Under the Hood — Update: Apple iPhone 3G exposed

http://www.eetimes.c[...]

2008-07-12

[66]

웹사이트

psRAM(HyperRAM)

https://www.cypress.[...]

Cypress semiconductor

[67]

웹사이트

Hyperbus

https://www.cypress.[...]

Cypress semiconductor

[68]

웹사이트

How to "open" microchip and what's inside? : ZeptoBars

http://zeptobars.com[...]

2012-11-15

[69]

문서

業界に痕跡を残して消えたメーカー DRAMの独自技術を持ちながらも倒産したQimonda

https://ascii.jp/ele[...]

[70]

문서

DRAM The Invention of On-Demand Data - IBM

https://www.ibm.com/[...]

[71]

서적

わかりやすい高密度記録技術

日刊工業新聞社

2008-09-28

[72]

웹사이트

集積回路工学第2 講義資料: 第12回: DRAM

http://ifdl.jp/akita[...]

金沢大学 理工学域

2022-01-15

[73]

문서

CCDに代わる画像素子として、1988年にMicron Technology社よりOptic RAMという商品名で発売された。

[74]

문서

米[[インテル]]は、[[磁気コアメモリ]]に代わるメモリとして、DRAM製造に着手していたが、ダイの状態では問題がないにもかかわらず、パッケージにするとソフトエラーが多発する問題に遭遇した。原因を究明すると、パッケージの[[セラミックス]]に[[アルファ線]]を放出する物質が含まれていることが判明した。インテルは、パッケージ製造元である[[京セラ]]に対して、この現象を極秘にするよう要請し、DRAM用パッケージは京セラが作った特注パッケージを使用した。そのため、インテル自身がインテル・1と呼ぶ半導体巨大企業へ発展する第一歩は、ソフトエラーの対策ノウハウを秘密にすることにより、市場から競合メーカーを追い出すことから始まったとされる。なお、この事実は、[[電子立国日本の自叙伝]] 単行本において、インテル自身によって解説された。

[75]

뉴스

世界最薄DRAM開発、エルピーダメモリ。本県で生産、出荷へ

http://www.47news.jp[...]

秋田魁新報

2011-06-23

[76]

서적

半導体とシステムLSI

日本実業出版社

2006-07-01

[77]

문서

韓国Samsung Electronics社は2009年6月17日に、サーバー向けにパッケージあたり16GビットのレジスタードDDR3モジュールを開発したと発表した。電源電圧は1.35Vで1つ4Gビットのダイを4枚内蔵している。

[78]

웹사이트

https://pc.watch.imp[...]

[79]

서적

マイクロプロセッサ テクノロジ

日経BP社

1999-12-06

[80]

문서

512Mビット(64M語×8、DDR2 667Mビット/秒)製品の価格が2006年11月は6.5米ドルだったものが2008年12月8日0.31米ドルまで低下した。

[81]

문서

2008年第算四半期の決算では、Samsung社が前年同期比約78%減ながら1,900億ウォンの営業利益を、Hynix社が4,650億ウォンの、エルピーダメモリ社が245億円の営業損失を報告した。

[82]

간행물

負の連鎖から脱出せよ

日経エレクトロニクス

2009-01-12

[83]

뉴스

JETROニュースページ 『半導体大手キマンダが倒産−1万人の雇用に影響か−(ドイツ)』

http://www.jetro.go.[...]

[84]

웹사이트

computerworld

http://www.computerw[...]

[85]

웹사이트

エルピーダメモリ産業活力の再生及び産業活動の革新に関する特別措置法の認定取得に関するお知らせ

http://www.elpida.co[...]

エルピーダメモリ株式会社

2011-02-12

[86]

뉴스

エルピーダが経営破綻 会社更生法の適用申請へ - MSN産経ニュース

https://web.archive.[...]

[87]

뉴스

Micron、エルピーダメモリの買収を完了 - PC Watch

https://pc.watch.imp[...]

[88]

뉴스

チキンゲーム勝者の笑顏…SKハイニックス、営業利益1兆ウォンの新記録 | Joongang Ilbo | 中央日報

https://web.archive.[...]

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com